Yep. Seems to be real:

Don’t Panic, ‘Wordle’ Hasn’t Run Out Of Five-Letter Words Just Yet share.google/5ApzE0CLR2Nh...

@clairexen.bsky.social

Neurodiverse Trans Geek Girl 🧙♀️ Queer Kinky Poly Mess 🏳️🌈 🏳️⚧️ CTO @YosysHQ 😺 RISC-V, SMT 👩💻 Opinions are my Ceti eel's 😛 ACAB BLM ✊ I am Antifa 🏴🚩 Vienna, Austria 📌 she/her 🧚♀️

Yep. Seems to be real:

Don’t Panic, ‘Wordle’ Hasn’t Run Out Of Five-Letter Words Just Yet share.google/5ApzE0CLR2Nh...

That was a repeat of the very first word

02.02.2026 16:57 — 👍 0 🔁 0 💬 1 📌 0

Wordle 1,689 3/6*

🟨🟨🟨🟨⬜

🟩🟨🟨🟨⬜

🟩🟩🟩🟩🟩

... Oh wow. Did we just reach "the end of wordle"? 🤔

Wordle 1,651 2/6*

⬜⬜🟩⬜🟩

🟩🟩🟩🟩🟩

🎉🎉🎉🎉🎉

Wordle 1,642 X/6*

🟨⬜🟩⬜🟨

🟩🟩🟩⬜🟩

🟩🟩🟩⬜🟩

🟩🟩🟩⬜🟩

🟩🟩🟩⬜🟩

🟩🟩🟩⬜🟩

Hahaha 😂😂😂

Wordle 1,641 4/6*

⬜⬜⬜🟨🟨

⬜🟩⬜🟨⬜

🟩🟩⬜🟩⬜

🟩🟩🟩🟩🟩

That. Was. So. F*ing. Hard.

Wordle 1,576 5/6*

⬜🟩🟩🟩🟩

⬜🟩🟩🟩🟩

⬜🟩🟩🟩🟩

⬜🟩🟩🟩🟩

🟩🟩🟩🟩🟩

Hahaha. Crazy...

![Slide from Hot Chips 2025:

"2025 TCMM Open Source Hardware Contribution Award:

Claire Wolf: In recognition of outstanding contributions to RISC-V —

including BitManip, RVFI, and PicoRV32—and to open-source tools like Yosys and IceStorm. [IEEE Computer Society TCMM / Technical Community on Microprocessors and Microcomputers]"](https://cdn.bsky.app/img/feed_thumbnail/plain/did:plc:egm6nnyusca4icjiqlb7pyiw/bafkreidgommoceirpkrigeshonoc5zmyhj2dnipsi5wngbl72z64ep3jze@jpeg)

Slide from Hot Chips 2025: "2025 TCMM Open Source Hardware Contribution Award: Claire Wolf: In recognition of outstanding contributions to RISC-V — including BitManip, RVFI, and PicoRV32—and to open-source tools like Yosys and IceStorm. [IEEE Computer Society TCMM / Technical Community on Microprocessors and Microcomputers]"

Congratulations @clairexen.bsky.social: #HotChips / IEEE TCMM 2025 Open Source Hardware Contribution Award

27.08.2025 01:33 — 👍 31 🔁 11 💬 2 📌 1

Wordle 1,529 4/6*

🟩⬜⬜🟩⬜

🟩⬜⬜🟩⬜

🟩⬜⬜🟩⬜

🟩🟩🟩🟩🟩

Wordle 1,518 3/6*

⬜⬜⬜⬜🟨

⬜🟩⬜⬜⬜

🟩🟩🟩🟩🟩

Wordle 1,517 6/6*

⬜🟨⬜🟨⬜

🟨⬜⬜⬜🟨

⬜🟨🟨🟩⬜

⬜⬜🟩🟩🟩

⬜⬜🟩🟩🟩

🟩🟩🟩🟩🟩

Ok. Wow. Uff. That was pretty exciting. I'm starting to think they are running out of good words..

Wordle 1,515 4/6*

⬜⬜⬜🟩🟩

⬜⬜⬜🟩🟩

🟨🟩🟨🟩🟩

🟩🟩🟩🟩🟩

Posting this for my 3rd guess 😜

So if you are currently involved with ISA-level decisions about inclusion of any pext/pdep-like instructions:

Please consider including SAG/inverse-SAG with bit-reversal of the goats.

No matter which of the two implementation methods you are using: All you need to do is not mask the goat bits.

So if you are currently involved with ISA-level decisions about inclusion of any pext/pdep-like instructions:

Please consider including SAG/inverse-SAG with bit-reversal of the goats.

No matter which of the two implementation methods you are using: All you need to do is not mask the goat bits.

At some point that patent will expire, and until then there's my implementation.

(And I think my approach will still stay relevant after, because it makes it very simple to build multi-cycle SAG cores.)

I think the really important takeaway is that they, my method and theirs, are both functionally the same, i.e. they both implement an SAG with bit-reversal of the goats.

This means, as far as the ISA is concerned, it's a safe decision to include an SAG instruction.

Wordle 1,498 4/6*

🟨⬜⬜⬜⬜

⬜🟩🟨⬜🟨

🟩🟩⬜⬜🟩

🟩🟩🟩🟩🟩

... back to normal ^__^

Nah! No luck. 🙈 I was unsure which of the 4 options I could come up with to pick, and as it turned out, it was none of them... 😂

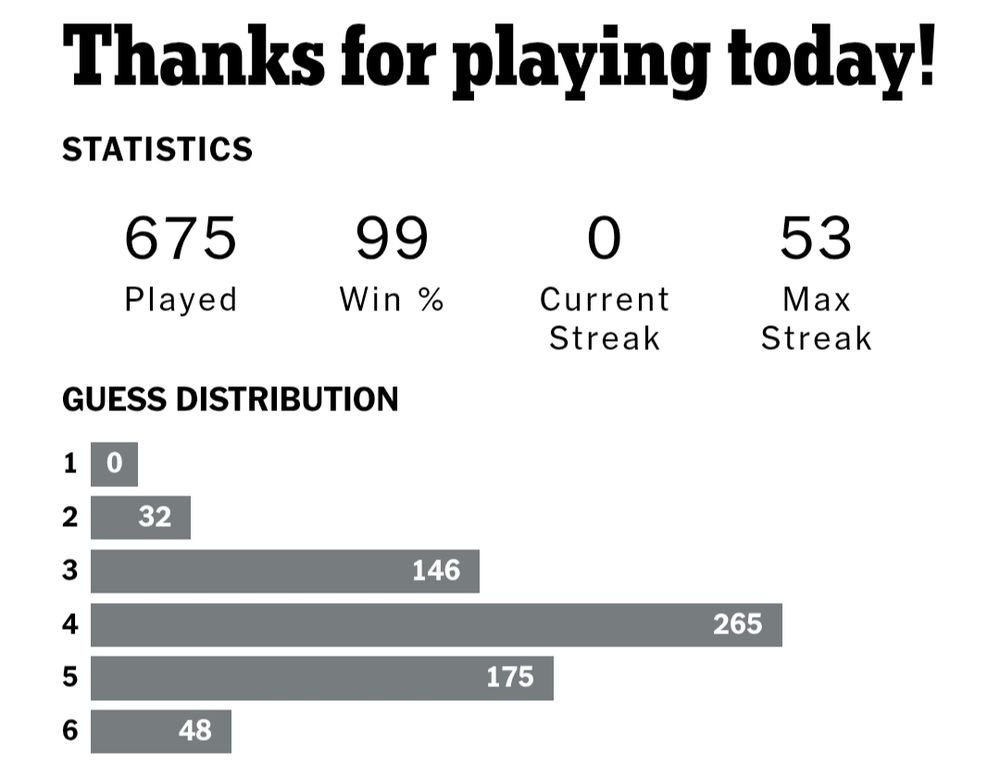

But I'm still at 99% and that's all that really matters to me. (But tbh, it does matter to me way more than it probably should..)

Wordle 1,497 X/6*

⬜⬜🟨🟩⬜

⬜🟩⬜🟩🟩

⬜🟩⬜🟩🟩

⬜🟩⬜🟩🟩

⬜🟩⬜🟩🟩

... Wahhh! I have ~23 hours to decide on a last guess... /o\

Here is the code:

github.com/clairexen/ed...

I can't see any obvious reason why that identity should not extend beyond 8-bit units. But I have not actually tested that hypothesis yet.

I have to make a correction regarding ☝️. I've now implemented the Hilewitz-Lee method as well in my edu-sag repository. And it implements the bit-reflecting-SAG as-is. All you have to do is to remove the '&ci' from the data input, thus it's always more area to implement PEXT than bit-reflecting-SAG.

24.07.2025 12:38 — 👍 1 🔁 1 💬 1 📌 0

Here is the code:

github.com/clairexen/ed...

I can't see any obvious reason why that identity should not extend beyond 8-bit units. But I have not actually tested that hypothesis yet.

I have to make a correction regarding ☝️. I've now implemented the Hilewitz-Lee method as well in my edu-sag repository. And it implements the bit-reflecting-SAG as-is. All you have to do is to remove the '&ci' from the data input, thus it's always more area to implement PEXT than bit-reflecting-SAG.

24.07.2025 12:38 — 👍 1 🔁 1 💬 1 📌 0

Wordle 1,483 4/6*

🟩⬜🟩⬜⬜

🟩⬜🟩🟨🟩

🟩🟩🟩⬜🟩

🟩🟩🟩🟩🟩

Wordle 1,482 6/6*

⬜⬜⬜⬜⬜

⬜⬜⬜⬜⬜

⬜⬜🟩🟩🟩

⬜🟩🟩🟩🟩

⬜🟩🟩🟩🟩

🟩🟩🟩🟩🟩

.. that was a bit unusual.

but I still got it in the end ^__^

Wordle 1,474 4/6*

⬜🟨⬜🟨⬜

🟨🟨🟨⬜⬜

🟩🟩⬜🟨⬜

🟩🟩🟩🟩🟩

Wordle 1,473 3/6*

⬜⬜⬜🟨⬜

🟩🟩⬜🟨🟨

🟩🟩🟩🟩🟩

Wordle 1,462 5/6*

⬜⬜🟩⬜⬜

⬜⬜🟩⬜🟩

⬜⬜🟩🟨🟩

⬜🟨🟩🟩🟩

🟩🟩🟩🟩🟩

I wrote a reference implementation for a SAG without bit reflection: github.com/clairexen/ed..., and I wrote a parametric SAG core for any bit width: github.com/clairexen/ed...

20.06.2025 16:04 — 👍 1 🔁 2 💬 0 📌 0

I wrote a reference implementation for a SAG without bit reflection: github.com/clairexen/ed..., and I wrote a parametric SAG core for any bit width: github.com/clairexen/ed...

20.06.2025 16:04 — 👍 1 🔁 2 💬 0 📌 0