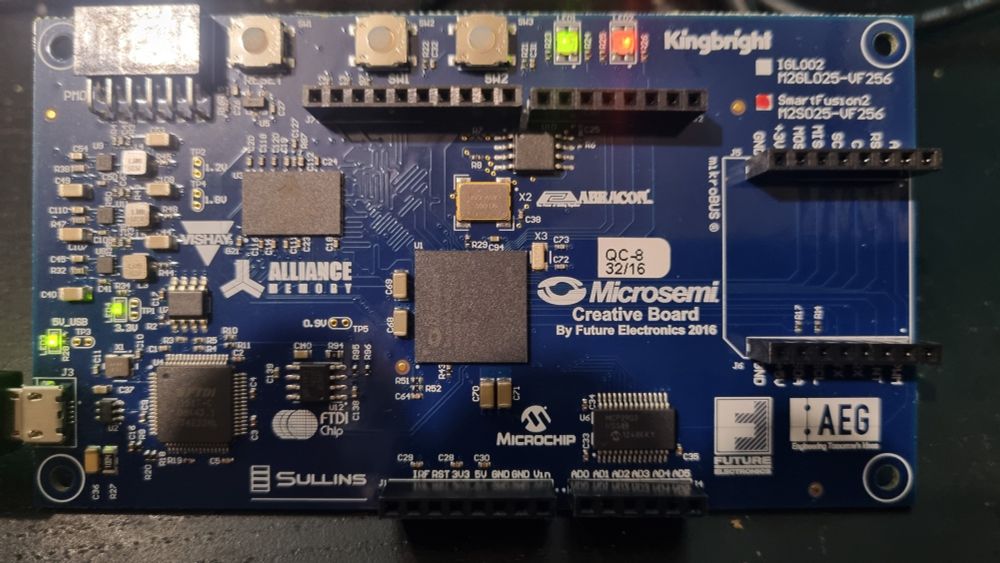

I bought two of these boards in 2016, one for a friend one for me. I forgot about mine until last night.

30.11.2024 18:29 — 👍 2 🔁 0 💬 0 📌 0

I bought two of these boards in 2016, one for a friend one for me. I forgot about mine until last night.

30.11.2024 18:29 — 👍 2 🔁 0 💬 0 📌 0Not yet it literally arrived this morning so I rushed to the office. But forgot it was the weekend they are changing internet providers so no net to do any work.

30.11.2024 12:51 — 👍 0 🔁 0 💬 1 📌 0

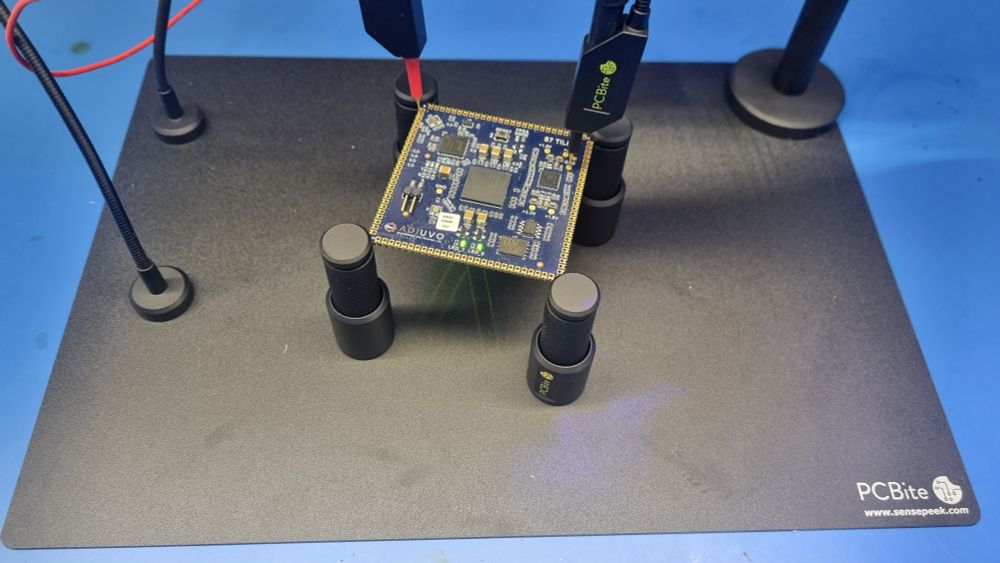

Quite impressed with the PCBite range from sensepeek. Came across them on a random tweet, it give the ability to probe with scopes, drive, observe digital signals and of course power boards hands free. Perfect for production test.

30.11.2024 12:14 — 👍 3 🔁 0 💬 2 📌 0

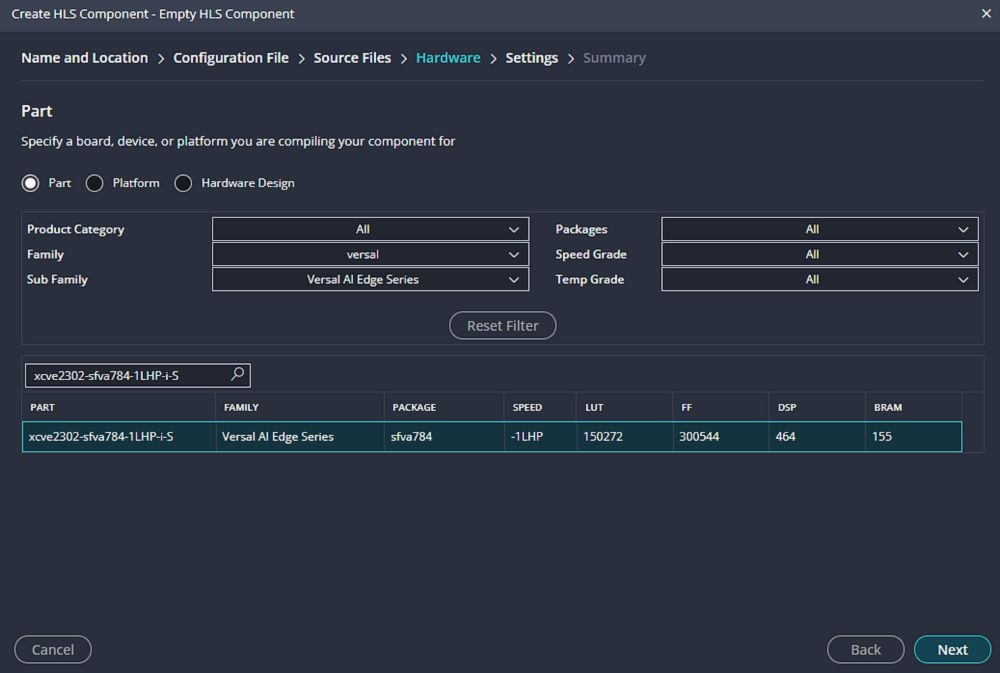

The ability to debug our FPGA applications is critical. This week I am looking at ChipScoPy, which enables us to leverage Python and Jupyter notebooks to work with ILAs, VIO and the hard debug peripherals in Versal devices.

www.adiuvoengineering.com/post/microze...

Fridays are for demos, so check out our latest Hackster project which shows how we can use a Arty A7, with MicroBlaze V, and Jupyter Labs to create a really cool robot arm demo we can control from our PC or program and replay sequences also

www.hackster.io/adam-taylor/...

Taking a look at creating an example design on the Agilex 5E development board.

#fpga #engineering #embeddedsystems #electronics #embeddedsoftware

www.adiuvoengineering.com/post/altera-...

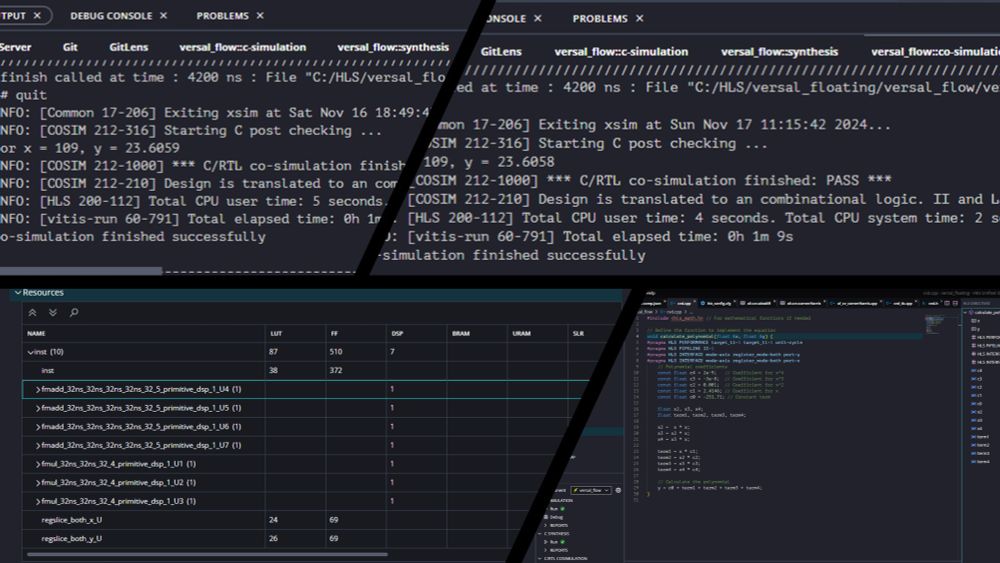

Looking this week at using a Vitis HLS to implement a DSP58 in FP32 mode

www.adiuvoengineering.com/post/microze...

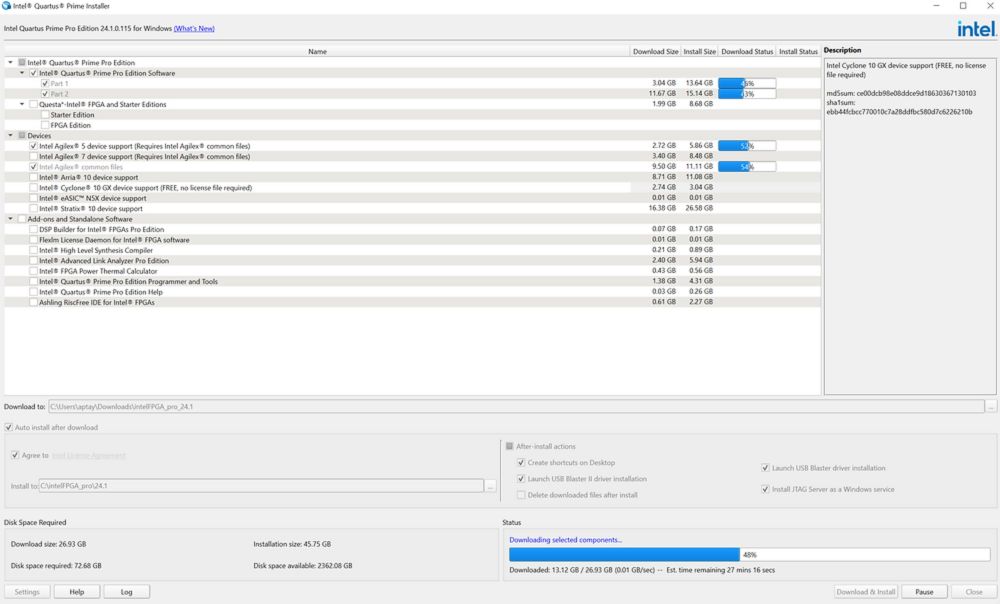

Taking a look at setting up the Agilex 5E tool chain and license.

www.adiuvoengineering.com/post/altera-...

I am very impressed with how Vitis Unified using the HLS flow has been able to target to the Versal DSP58 in FP32 mode for the equation I was implementing in last weeks blog. Significantly less resources than required using the native VHDL 2008 float package.

18.11.2024 19:44 — 👍 1 🔁 0 💬 0 📌 0

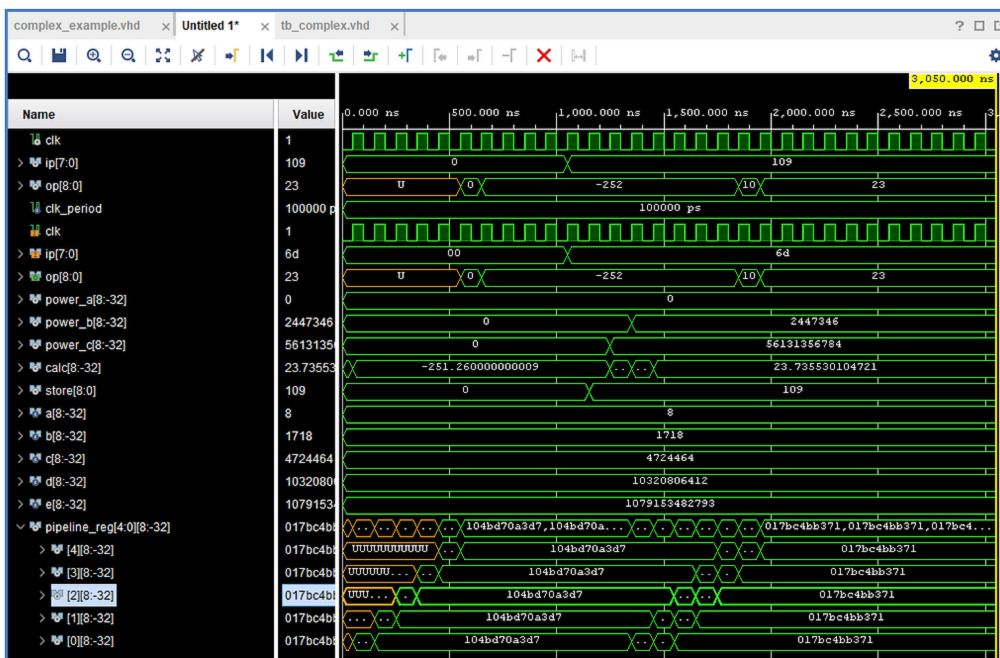

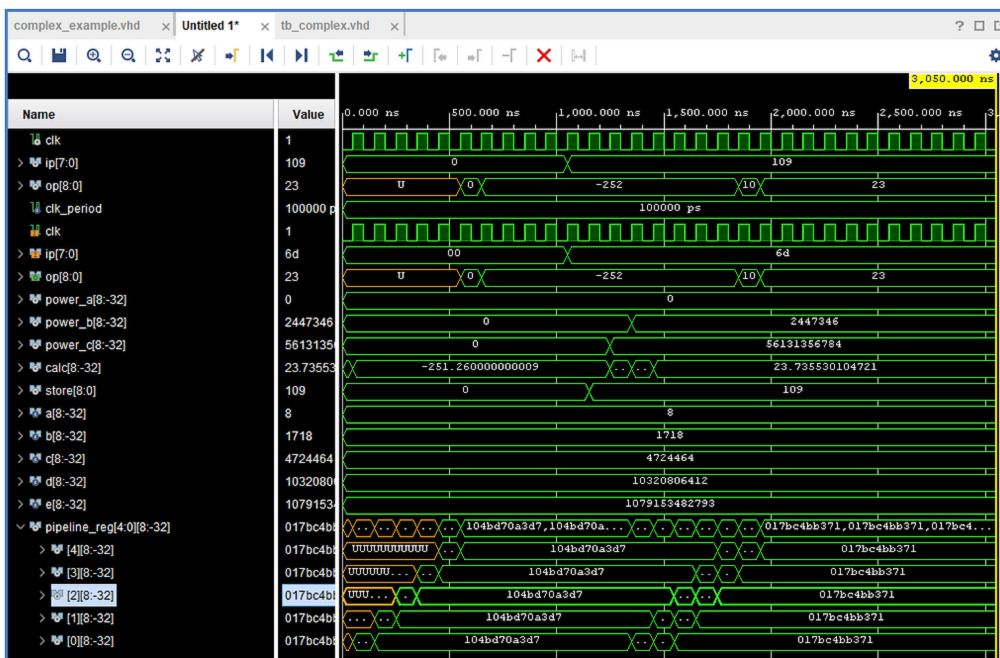

This week I was taking a look at the differences in resources required to implement the same algorithm when using the VHDL 2008 fixed and floating point packages.

www.adiuvoengineering.com/post/microze...

Always wanted do Jury service but never have. I am an expert witness in a patent cases and that clashes with a conference I want to go to next year. Enjoy Supercomputing.

13.11.2024 17:37 — 👍 1 🔁 0 💬 0 📌 0

Last week we ran a webinar on implementing maths in FPGA. One of the attendees asked the question what the difference in implementation size would be between fixed and floating point.

#fpga #embeddedsystems #engineering #embeddedsoftware #engineering

www.adiuvoengineering.com/post/microze...