One of those drivers that refuses to let faster cars pass

09.08.2025 01:32 — 👍 5 🔁 2 💬 2 📌 0@reflexive.space.bsky.social

he/him (John), near-30, looking for work! 🌙 your nonlocal hacker friend 🦀 hw/fw/sw, security, microarchitecture, rust, etc 🐬 hacks on gc/wii/melee stuff sometimes 🐘 @eigenform@treehouse.systems 🐦 @eigenform

One of those drivers that refuses to let faster cars pass

09.08.2025 01:32 — 👍 5 🔁 2 💬 2 📌 0wwhat the

08.08.2025 04:02 — 👍 1 🔁 0 💬 0 📌 0kinda tangential but: apart from the undercurrent of anthropogenic climate change, i wonder whether or not there are any meaningful correlations between the 2022 tonga eruption and anomalies in the recent/coming years

06.08.2025 20:03 — 👍 1 🔁 0 💬 0 📌 0

screenshot of part of apple's mac store configuration screen: Chip (Processor) Which chip is right for you? Apple M4 Max chip with...

I'm glad they clarify "Chip (Processor)" otherwise I might've thought they were talking about a tasty snack

05.08.2025 23:24 — 👍 293 🔁 18 💬 17 📌 2hopefully unrelated to speculative store bypass disable, otherwise things are gonna get confusing

05.08.2025 17:57 — 👍 0 🔁 0 💬 1 📌 0holy smokes bsky.app/profile/weat...

30.07.2025 00:57 — 👍 0 🔁 0 💬 0 📌 0"Reverse faulting events of the size of the July 29, 2025, earthquake are typically about 130 km by 65 km in size (length x width)." goddamn..

30.07.2025 00:40 — 👍 0 🔁 0 💬 1 📌 0(this is apparently false! the actual paper describes a case where STLF occurs for a faulting load and matches a store queue entry written by a privileged store - then you infer the value by timing instrs dependent on the load)

29.07.2025 22:47 — 👍 1 🔁 0 💬 0 📌 0alias gs='git status ' 🫵

29.07.2025 17:04 — 👍 6 🔁 0 💬 0 📌 0started watching foundation and god i love lee pace

26.07.2025 04:21 — 👍 0 🔁 0 💬 0 📌 0speculatively fetching and executing a beer 🤙

23.07.2025 22:05 — 👍 1 🔁 0 💬 0 📌 0😠

20.07.2025 20:54 — 👍 0 🔁 0 💬 0 📌 0do i know any people who:

(a) have modern web development experience

(b) like #GlasgowInterfaceExplorer or just want to do something fairly simple and useful

(c) want to work with me on a new piece of the project?

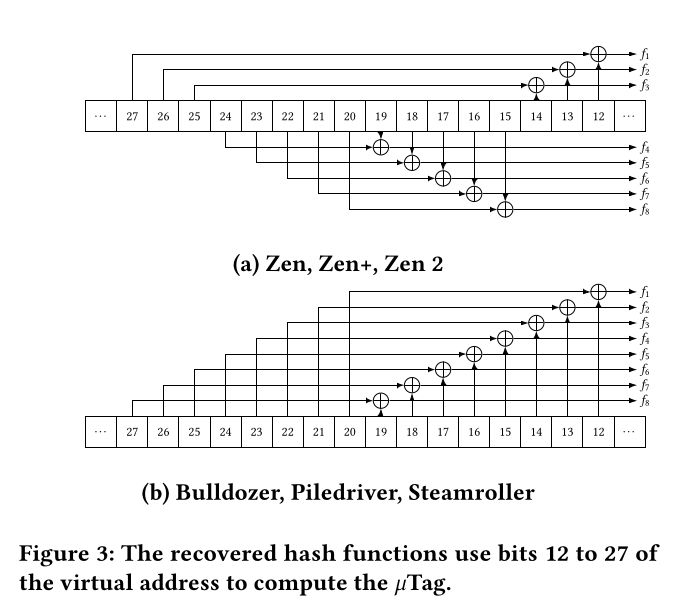

Figure 3. from the paper "Take A Way: Exploring the Security Implications of AMD’s Cache Way Predictors"

figure from the paper (for comparison to the `inp_diff` field in the previous image) \o/ neat!

14.07.2025 19:04 — 👍 2 🔁 0 💬 0 📌 0

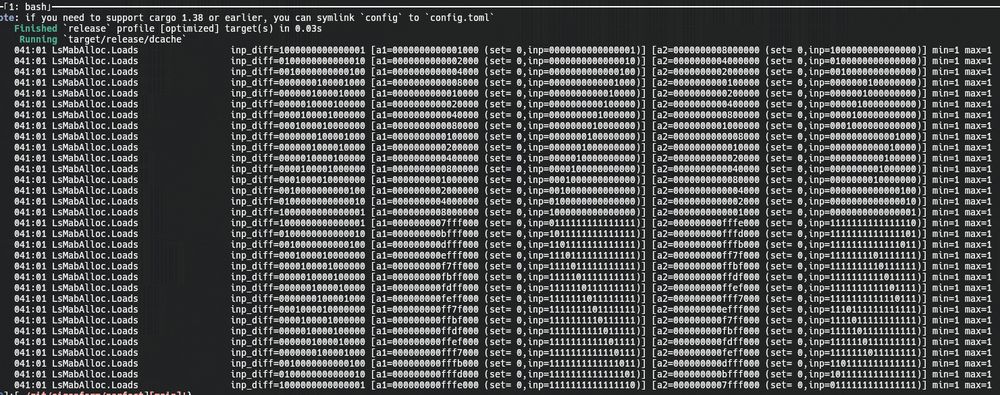

Command-line output showing consistent miss address buffer (MAB) allocations for a load instruction caused by L1D way predictor misses on a Zen 2 core. Each line in the output represents a pair of virtual addresses whose micro-tag is colliding, necessarily resulting in a misprediction. The `inp` fields are bits in the addresses used as input to a simple hash function which associates each virtual address to the cache way used in the previous load from that address. The `inp_diff` fields visually show us which pairs of bits are being XORed together!

false alarm, i was apparently only iterating through 12 bits instead of all 16 bits of input! \o/ i think this works

14.07.2025 18:51 — 👍 0 🔁 0 💬 1 📌 0wikichip down again? v.v

14.07.2025 17:09 — 👍 0 🔁 0 💬 0 📌 0maybe i should be randomizing the high bits or something, kinda just ignoring them

10.07.2025 21:55 — 👍 0 🔁 0 💬 1 📌 0(the SOG mentions that fill requests should occur in either case when the utag is wrong, so i dont think it's because i'm failing to miss/hit in L2...)

10.07.2025 21:53 — 👍 0 🔁 0 💬 1 📌 0*also it should happen when i flip bit 19 but it doesnt? :^(

10.07.2025 21:49 — 👍 0 🔁 0 💬 1 📌 0adding a thing to `perfect` for trying to create zen2 l1d way predictor misses, but it seems like MAB allocs for the loads only occur reliably when xoring bits 15/20, 16/21, 17/22, and 18/23 yields 1? but the takeaway paper mentions the hash includes bits 12/27, 13/26 and 14/25 too? wuhhh

10.07.2025 21:46 — 👍 0 🔁 0 💬 1 📌 0i guess this is basically: you can make inferences based on L1 utag hits and stlf hits?

08.07.2025 21:27 — 👍 0 🔁 0 💬 0 📌 0at least theres no *values* leaking here afaict www.amd.com/content/dam/...

08.07.2025 21:24 — 👍 1 🔁 0 💬 2 📌 0i dont usually do hats.. but maybe i should??

06.07.2025 19:58 — 👍 1 🔁 0 💬 0 📌 0

it me

happy sunday bsky

06.07.2025 19:56 — 👍 7 🔁 0 💬 1 📌 0so trueeee

04.07.2025 19:22 — 👍 1 🔁 0 💬 0 📌 0longjmp implies the existence of floatjmp and doublejmp

02.07.2025 22:19 — 👍 54 🔁 12 💬 6 📌 0this kind of dense, walkable control flow graph is illegal to build in most american compilers

03.07.2025 04:36 — 👍 164 🔁 18 💬 3 📌 2they should make longjmp2, a new and more fucked up longjmp variant

02.07.2025 21:04 — 👍 51 🔁 8 💬 6 📌 1