Thanks. I'm glad it's useful to you! As for the pointers, you remind me that I should post the CDC version of this FIFO, which indeed does non-2^N pointers across clock domains, without using Grey Codes. ;)

good luck with your projects!

25.06.2025 13:53 — 👍 1 🔁 0 💬 0 📌 0

I have an open client slot for FPGA design consulting: fpgacpu.ca/gateforge/in...

Over the last 9 years, I've built control loops for nanotech research, DSP accelerators for medical, custom 10 Gb/s sensor for a satellite, video processing, industrial control, and radiation exposure testing.

23.06.2025 13:15 — 👍 0 🔁 1 💬 0 📌 0

Pipeline FIFO Buffer

Decouples two sides of a ready/valid handshake to allow back-to-back transfers without a combinational path between input and output, thus pipelining the path to improve concurrency and/or timing. *An...

Here's a common workhorse for designs: a Pipeline FIFO Buffer. Any FIFO depth is allowed, not only powers-of-2. The input-to-output latency is 2 cycles. Can function as a Circular Buffer. The tricky bit in this FIFO design is the read output, which is registered for speed.

fpgacpu.ca/fpga/Pipelin...

23.06.2025 13:15 — 👍 1 🔁 0 💬 1 📌 0

GateForge Consulting Ltd.

I have an open client slot for FPGA design consulting: fpgacpu.ca/gateforge/in...

Over the last 9 years, I've built control loops for nanotech research, DSP accelerators for medical, custom 10 Gb/s sensor for a satellite, video processing, industrial control, and radiation exposure testing.

11.06.2025 13:52 — 👍 2 🔁 1 💬 0 📌 0

Pipeline Half Buffer

A single pipeline register with ready/valid handshakes. Decouples the input and ouput handshakes (no combinational path), but does not allow concurrent read/write like a full [Pipeline Skid Buffer](....

A Pipeline Half-Buffer: A single pipeline register with ready/valid handshakes. Decouples the input and ouput handshakes (no combinational path), but does not allow concurrent read/write like a full Pipeline Skid Buffer.

fpgacpu.ca/fpga/Pipelin...

10.06.2025 15:43 — 👍 3 🔁 1 💬 0 📌 0

Pipeline Skid Buffer

Decouples two sides of a ready/valid handshake to allow back-to-back transfers without a combinational path between input and output, thus pipelining the path. *Can function as a two-entry Circular Bu...

Here's the most important pipeline building block: a Skid Buffer. It decouples two sides of a ready/valid handshake to allow back-to-back transfers without a combinational path between input and output, thus fully pipelining the path.

fpgacpu.ca/fpga/Pipelin...

03.06.2025 18:51 — 👍 2 🔁 0 💬 0 📌 0

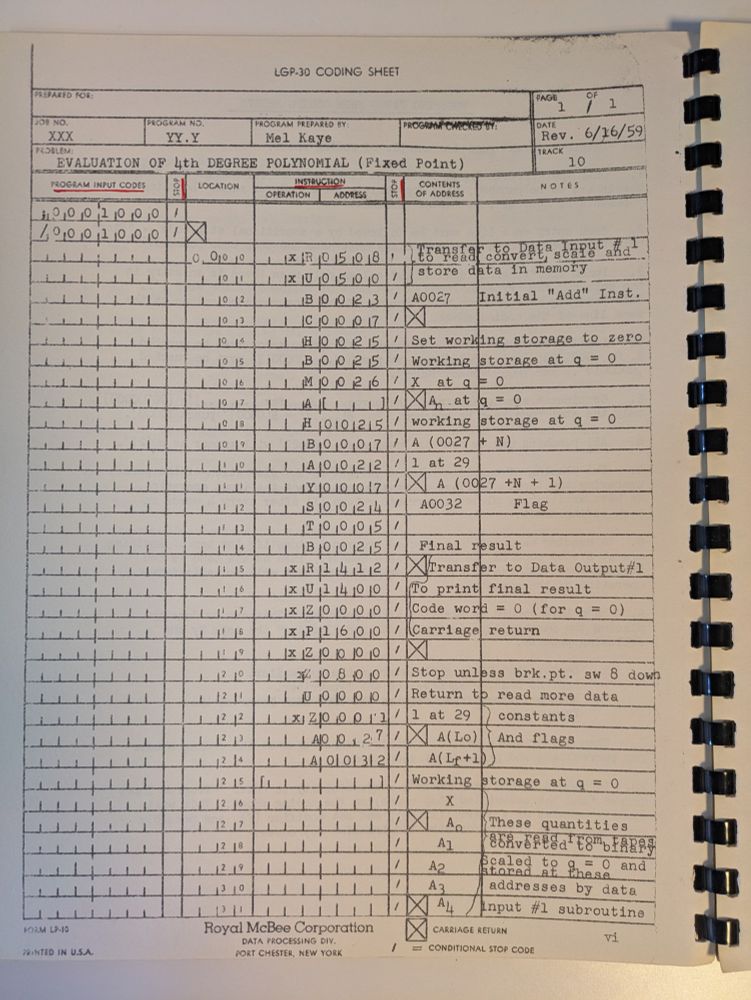

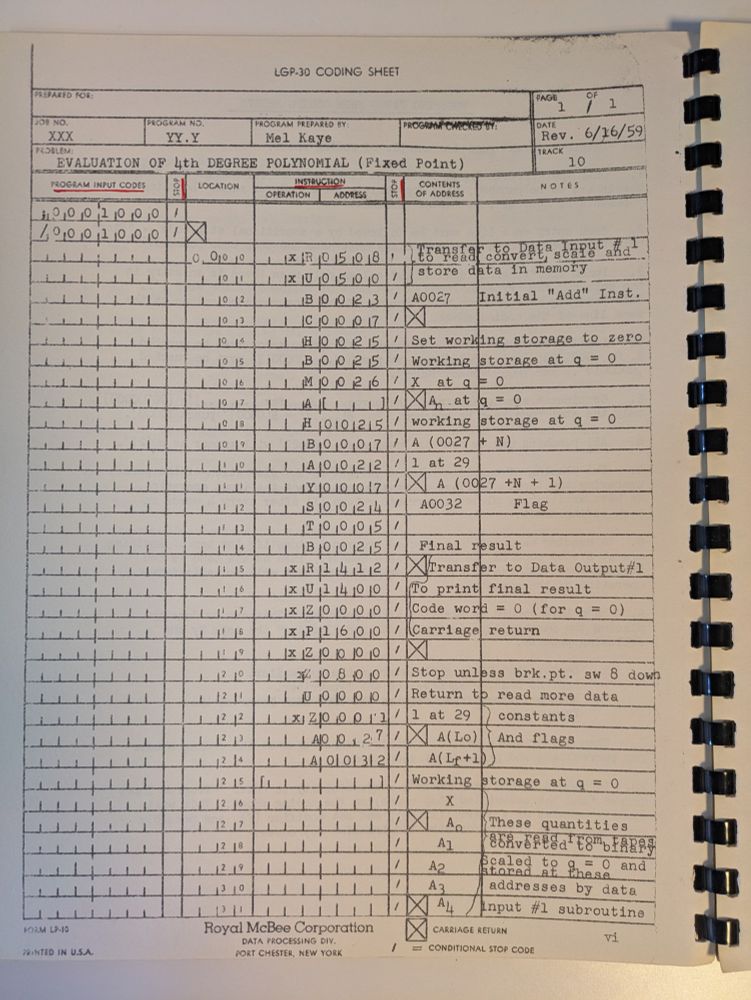

Had to show off for a sec. :) I was amazed when I found that manual at a used book store. So yes, we have examples of Mel's code.

05.02.2025 19:02 — 👍 0 🔁 0 💬 0 📌 0

Ah yes. This Mel. :)

05.02.2025 17:55 — 👍 2 🔁 0 💬 1 📌 0

This looks like something that would have been possible in the era of delay-line memory. The programming and I/O would have been tricky, but the hardware so minimal and reliable (given vacuum tubes).

05.02.2025 16:30 — 👍 3 🔁 0 💬 2 📌 0

I wonder how much of that comes from legacy Verilog-1995 codebases, which is really too limited a language for modern hardware design. (I hold to a subset of the synthesizable subset of Verilog-2001. Modularization takes care of the rest.)

18.01.2025 19:02 — 👍 0 🔁 0 💬 0 📌 0

As I struggled today with an FPGA CAD tool's IP code generation and management, it occurred to me that I haven't needed to write HDL-generating code for years now. Extreme modularization, along with generate blocks and parameters, has always sufficed, even for 20k+ line designs.

16.01.2025 23:29 — 👍 2 🔁 0 💬 2 📌 0

Bit twiddling hacks are "neat tricks" in software, but they are often branch-free and need no allocated memory, so they map naturally to hardware design.

More listed here: fpgacpu.ca/fpga/reading...

02.12.2024 19:15 — 👍 9 🔁 3 💬 0 📌 0

Deserializer Differential N to 2N

This module extends the [1-to-N Differential Deserializer](./Deserializer_Differential_1toN.html) by packing two differential N-bit deserialized words into one differential 2N-bit word and extending ...

Here is a module which extends the 1-to-N Differential Deserializer by packing two consecutive differential N-bit deserialized words into one differential 2N-bit word and extending the bitslip word-alignment logic to support this double-width word. fpgacpu.ca/fpga/Deseria...

23.09.2024 13:25 — 👍 0 🔁 0 💬 0 📌 0

Register Pipeline Variable

Delays a pipeline with variable shift-registers to adjust the latency from input to output. The latency, in clock cycles, from input to output is selected by the `tap_number` control input, and has a...

When aligning multiple data channels, you need to pass them through variable-delay shift registers. This is where using an FPGA's built-in shift-register hardware is a must, since using LUTs+FFs ends up being the large majority of the deserializer area!

fpgacpu.ca/fpga/Registe...

18.09.2024 13:35 — 👍 1 🔁 0 💬 0 📌 0

Pipeline Serial Parallel

Reads in multiple serial words (most-significant word first) and signals when the last input word has been read-in and a new, wider output word is ready to be read-out, in the same cycle if necessary ...

A pipeline serial to parallel converter. Reads in multiple serial words and signals when the last input word has been read-in and a new, wider output word is ready to be read-out, in the same cycle if necessary to receive an uninterrupted serial stream.

fpgacpu.ca/fpga/Pipelin...

16.09.2024 12:47 — 👍 1 🔁 0 💬 0 📌 0

Deserializer Differential 1toN

Takes in a serial differential data stream, at single or double data rate, and deserialises it as parallel words of both positive and negative polarity. The input delays on the negative and positive ...

A deserializer for differential data, with a configurable 1:N ratio, SDR or DDR data rate, and independent positive and negative data polarity input delays and deserializers, which enable bit and word alignment training later on.

fpgacpu.ca/fpga/Deseria...

10.09.2024 15:36 — 👍 0 🔁 0 💬 0 📌 0

fpgacpu.ca

Charles Eric LaForest, PhD operates fpgacpu.ca as a resource about FPGAs, computer history, and computer architecture.

fpgacpu.ca now supports HTTPS! It's still a static site without cookies or Javascript or any inputs, but I was getting reports of problems with browsers, corporate networks, and Google not liking the absence of SSL. Enjoy more easily now!

05.09.2024 13:22 — 👍 2 🔁 0 💬 0 📌 0

GateForge Consulting Ltd.

I have an open slot for a client at this time.

Let's discuss your FPGA design needs!

fpgacpu.ca/gateforge/in...

I'm a consultant doing primarily logic design on FPGAs and related full-stack software development for clients who need application-specific processing for their products.

27.08.2024 01:23 — 👍 0 🔁 0 💬 0 📌 0

GateForge Consulting Ltd.

I have an open slot for a client, starting *immediately*. Let's discuss your FPGA design needs! fpgacpu.ca/gateforge/in...

I'm a consultant doing primarily logic design on FPGAs and related full-stack software development for clients who need application-specific processing for their products.

07.08.2024 02:38 — 👍 0 🔁 0 💬 0 📌 0

Clock Switchover

To be used to control a PLL or MMCM with two clock inputs, where the primary clock runs always, and a secondary clock eventually begins operating and replaces the primary clock, for example when we ne...

In one project, I had to first configure an external device before it could generate it's own source-synchronous clock for data and control. This Clock Switchover module detects when the device data clock becomes active and stable and handles clock selection and reset.

fpgacpu.ca/fpga/Clock_S...

14.06.2024 14:20 — 👍 0 🔁 0 💬 0 📌 0

GateForge Consulting Ltd.

I have an open slot for a client, starting in the last week of July. Let's discuss your needs! fpgacpu.ca/gateforge/in...

I'm a consultant doing logic design on FPGAs and related software development (from kernel up to application) for clients who need application-specific processing.

13.06.2024 15:30 — 👍 1 🔁 0 💬 0 📌 0

Accumulator Binary Saturating

Adds/subtracts the signed `increment_value` to the signed `accumulated_value` when `increment_valid` is pulsed high *for one cycle*. A new increment may be added when `increment_done` pulses high, in ...

We can now build a saturating accumulator with variable upper/lower limits. I used this as the Integral term of a PID controller, where the limits are dynamically adjusted to limit integral wind-up, which makes the PID controller recover from saturation faster.

fpgacpu.ca/fpga/Accumul...

13.06.2024 13:12 — 👍 0 🔁 0 💬 0 📌 0

Adder Subtractor Binary Saturating

A signed saturating integer adder/subtractor, with `carry_in`, `carry_out`, internal `carries` into each bit. The operation is selected with `add_sub`: setting it to 0 for an add (A+B), and to 1 for ...

Here's a Saturating Adder/Subtractor. The limits can be any signed numbers, even dynamically variable. One use is as the final stage of a PID controller, so we can guarantee the output never wraps around and flips sign suddenly, which would be catastrophic.

fpgacpu.ca/fpga/Adder_S...

11.06.2024 13:06 — 👍 0 🔁 0 💬 0 📌 0

Arithmetic Predicates Binary

Given two integers, `A` and `B`, derives all the possible arithmetic predictates (equal, greater-than, less-than-equal, etc...) as both signed and unsigned comparisons.

With an Subtractor that provides the carry-out and the overflow, we can create an Arithmetic Predicates module which computes all possible signed and unsigned comparisons of two numbers. This way we don't have to worry about getting RTL arithmetic right each time.

fpgacpu.ca/fpga/Arithme...

10.06.2024 14:37 — 👍 1 🔁 0 💬 0 📌 0

Adder Subtractor Binary

A signed binary integer adder/subtractor, with `carry_in`, `carry_out`, `overflow`, and all the intermediate `carries` into each bit position (see [Carry-In Calculator](./CarryIn_Binary.html) for thei...

And with those previous modules, we can now build an adder/subtractor module. It's much more complex than usual, but it also gives us all bit carries and the overflow bit, and is independent of Verilog's signed/unsigned arithmetic behaviour.

fpgacpu.ca/fpga/Adder_S...

07.06.2024 13:16 — 👍 1 🔁 0 💬 0 📌 0

Width Adjuster

Takes in a vector of a given input width, a flag denoting if it is a signed/unsigned value, and an output width. Outputs the same vector extended or truncated to the output width, with signed/unsigned...

Let's build up to some saturating arithmetic logic. Here's a Width Adjuster, which either extends (optionally signed) or truncates values. I often use it to normalize widths of misc. signals before packing/unpacking/multiplexing/arithmetic/etc...

fpgacpu.ca/fpga/Width_A...

05.06.2024 12:29 — 👍 1 🔁 0 💬 0 📌 0

Pipeline Credit Gate

Gates a pipeline if the internal credit count is zero. A separate pulse input adds one credit per pulse. Continuous, multi-cycles pulses are allowed. Each completed pipeline handshake from input to ou...

Here's a Pipeline Credit Gate. It let's handshakes complete only if there are available credits, which are added via external pulses and subtracted by each completed handshake. It can ensure that an operation is only considered complete after N items have been read out.

fpgacpu.ca/fpga/Pipelin...

03.06.2024 14:06 — 👍 1 🔁 0 💬 0 📌 0

Rules for Ready/Valid Handshakes

A set of rules for consistent and high-performance designs with ready/valid handshakes, and a discussion of the underlying synchronization mechanism.

I've updated my "rules for ready/valid handshakes" to describe both a control implementation I made heavy use of in the past year, and to add discussion on the synchronization operation which underlies ready/valid handshakes, much like ready/valid handshakes underlie AXI4.

fpgacpu.ca/fpga/handsha...

31.05.2024 13:06 — 👍 3 🔁 2 💬 0 📌 0

The official bluesky account of Foxes In Love!

vintage computers, tubes, the MOnSter6502, cross-sectioned electronic parts, capacitors, and other detritus. coauthor of http://nostarch.com/open-circuits

BA-Psych, MMath-CompSci

Ottawa CANADA 🇨🇦

Home: www.idallen.com

Contact Improvisation Dance: www.contactimprov.ca

Former college professor of Free/Libre GNU+Linux @ teaching.idallen.com

Improve democracy www.fairvote.ca

Defend digital freedom www.eff.org

Computer history. Reverse-engineering old chips. Restored Apollo Guidance Computer, Alto. Ex-Google, Sun, Msft. So-called boffin.

Please tweet at me with CUDA performance tips.

Kilocore RISC-V FPGA accelerators; former Microsoft dev tools architect; Vice-chair RISC-V SoftCPU SIG & Composable Custom Extensions Task Group; blog: https://fpga.org. Cyclist. Let's try kindness. 🇨🇦-🇺🇸

Neurodiverse Trans Geek Girl 🧙♀️

Queer Kinky Poly Mess 🏳️🌈 🏳️⚧️

CTO @YosysHQ 😺 RISC-V, SMT 👩💻

Opinions are my Ceti eel's 😛

ACAB BLM ✊ I am Antifa 🏴🚩

Vienna, Austria 📌 she/her 🧚♀️