Rubin CPX looks very similar to GB202, at least in the image Nvidia released. Could be very well a full GPU, with raster engines, PCI-Expess and display outputs. While unlikely, it might be how the RTX 6090 will look like.

11.09.2025 10:25 — 👍 4 🔁 1 💬 1 📌 0

#Intel #GraniteRapids SKU stack:

cdrdv2-public.intel.com/860027/Intel...

16.07.2025 08:26 — 👍 4 🔁 3 💬 0 📌 0

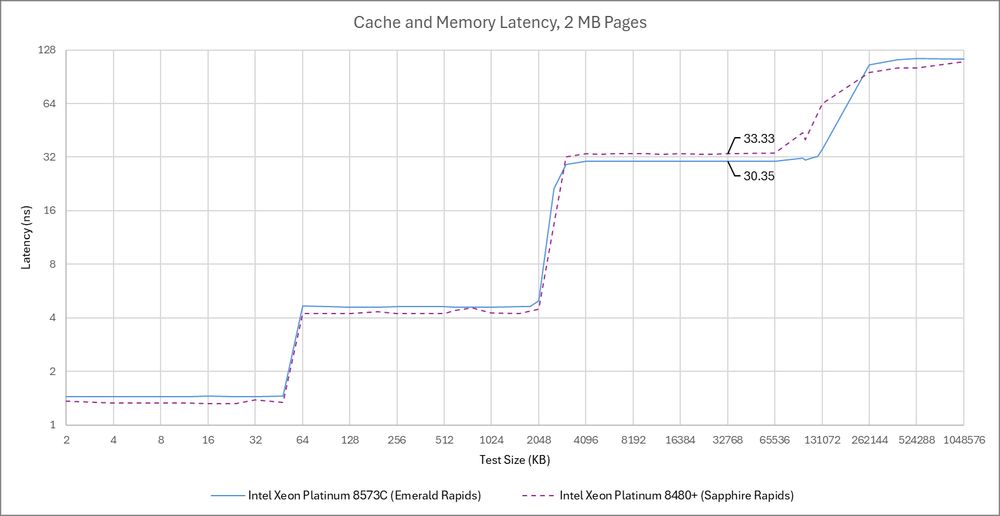

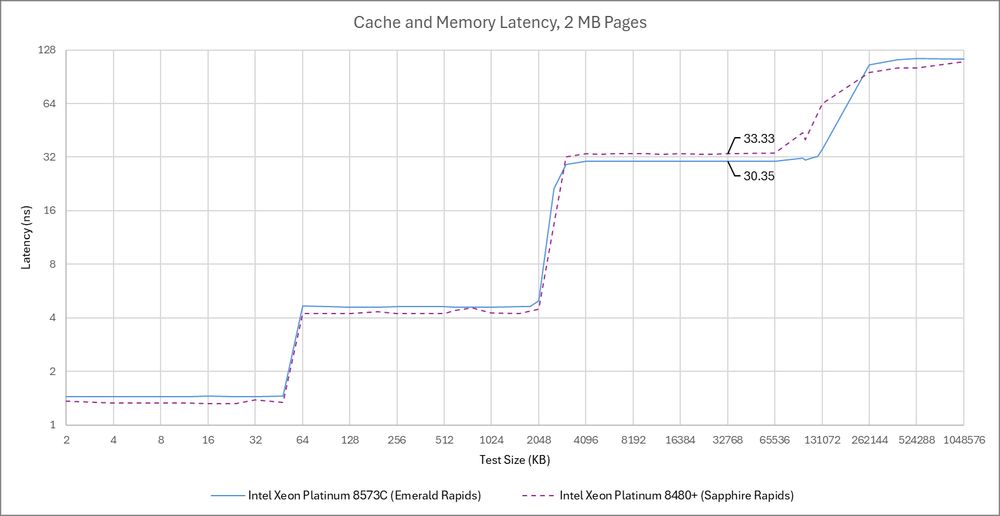

Intel's newer Emerald Rapids improves L3 latency compared to Sapphire Rapids, at least when one core is able to allocate a similar amount of L3 capacity. It's still high at ~105 core cycles, but better than ~125 cycles from the last generation.

11.07.2025 22:36 — 👍 2 🔁 2 💬 1 📌 0

Fake website servic welcome page. text reads:

"Your favorite tool is now ruined by AI"

"you might not like it but shareholders love it"

when you open a service you've been using for a decade only to find it out it caught the virus

05.07.2025 17:52 — 👍 15535 🔁 5992 💬 60 📌 85

oh and fuck Future, PLC. they are the ones that killed AnandTech as well.

01.07.2025 18:48 — 👍 3 🔁 1 💬 1 📌 0

YouTube video by Nordic Game Jam

Quaternions - Freya Holmer | NGJ2025

my NGJ2025 talk about Quaternions is up! 💫

www.youtube.com/watch?v=PMvI...

03.06.2025 20:39 — 👍 474 🔁 52 💬 18 📌 5

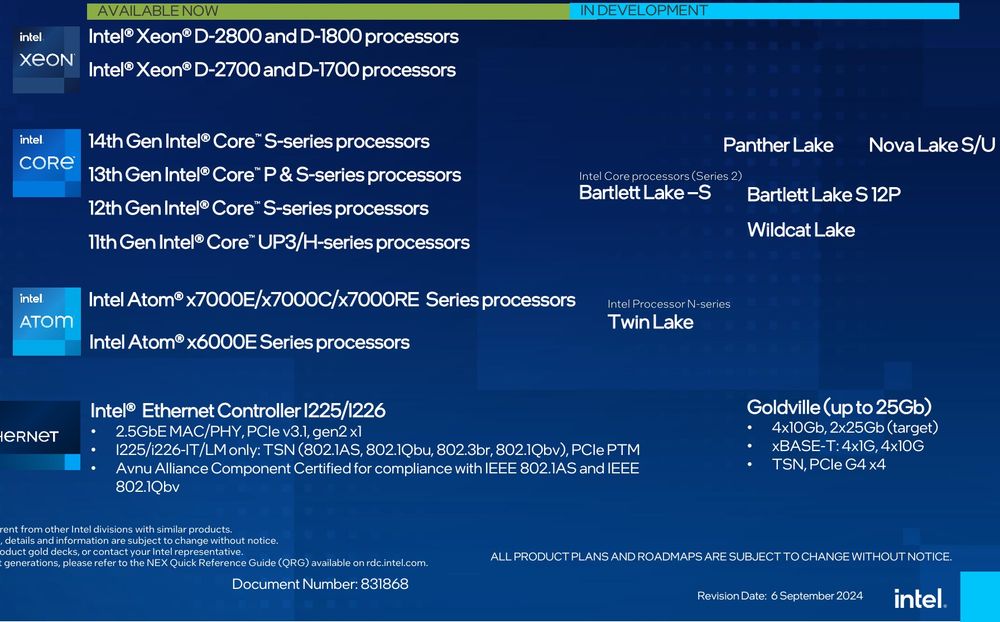

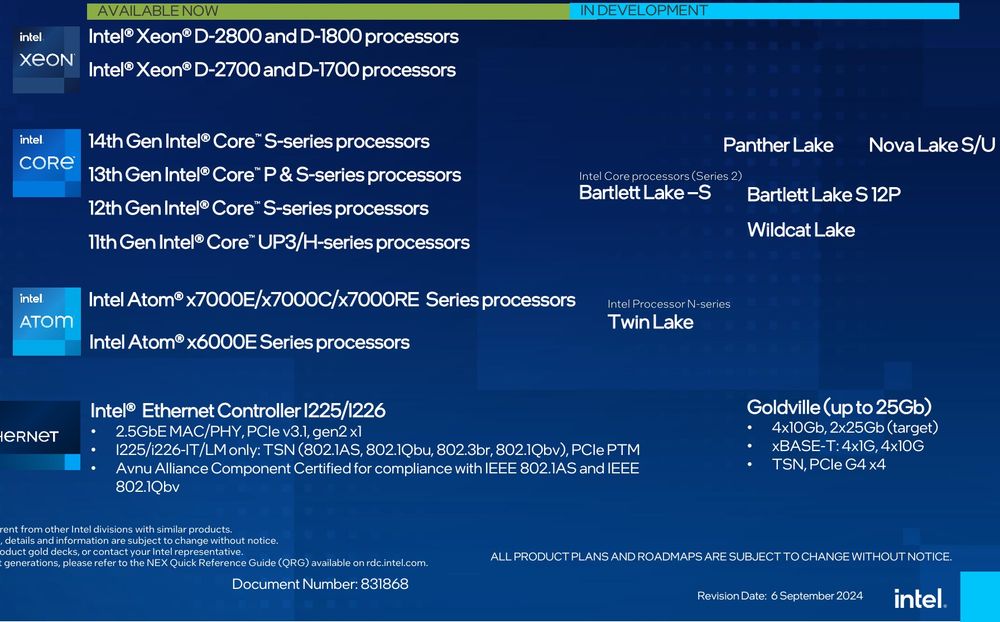

An Intel slide with #NovaLakeU, #NovaLakeS, #WildcatLake, P-Only #BartlettLake:

www.intel.com/content/www/...

14.05.2025 15:57 — 👍 2 🔁 2 💬 0 📌 0

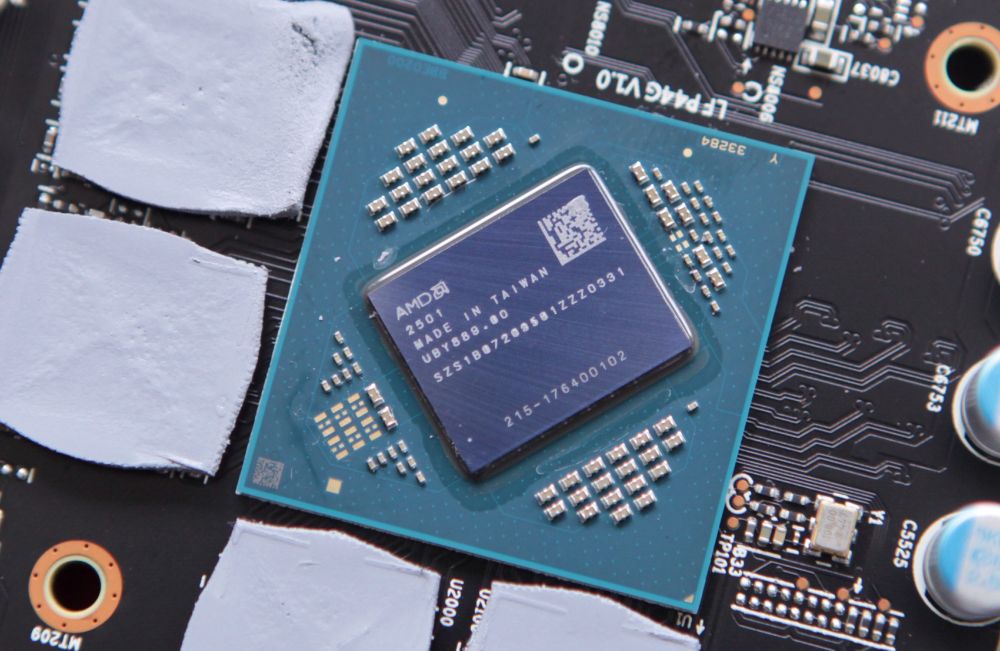

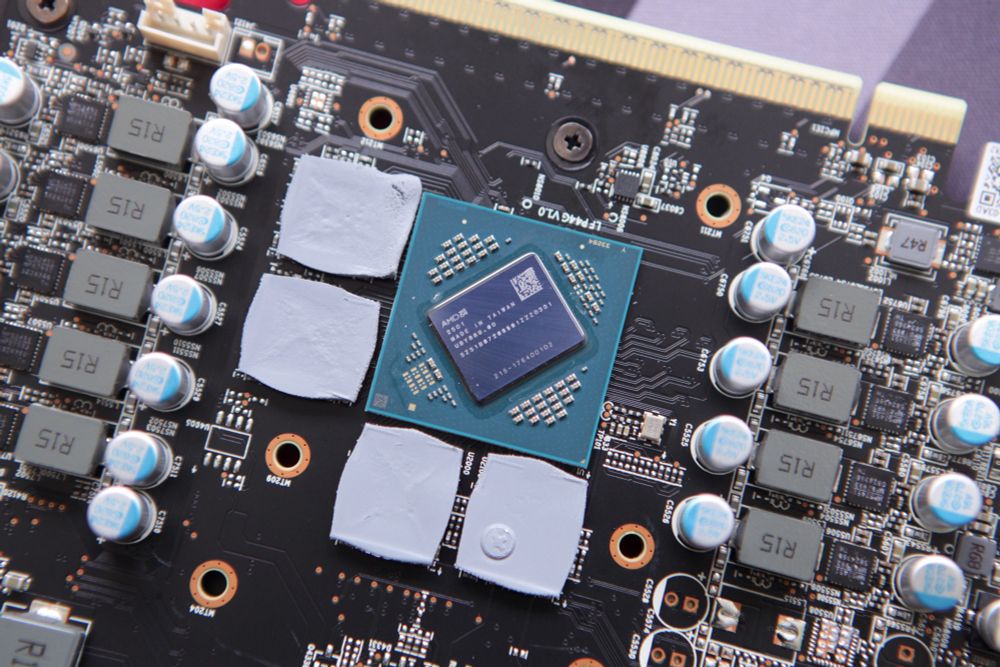

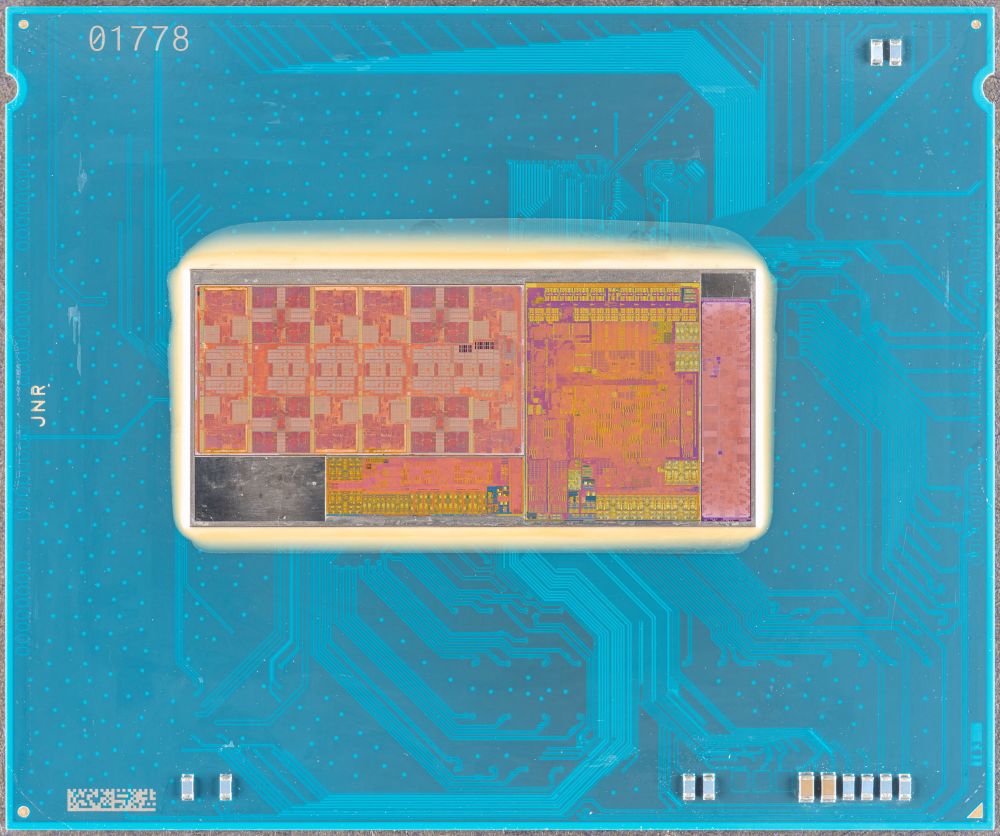

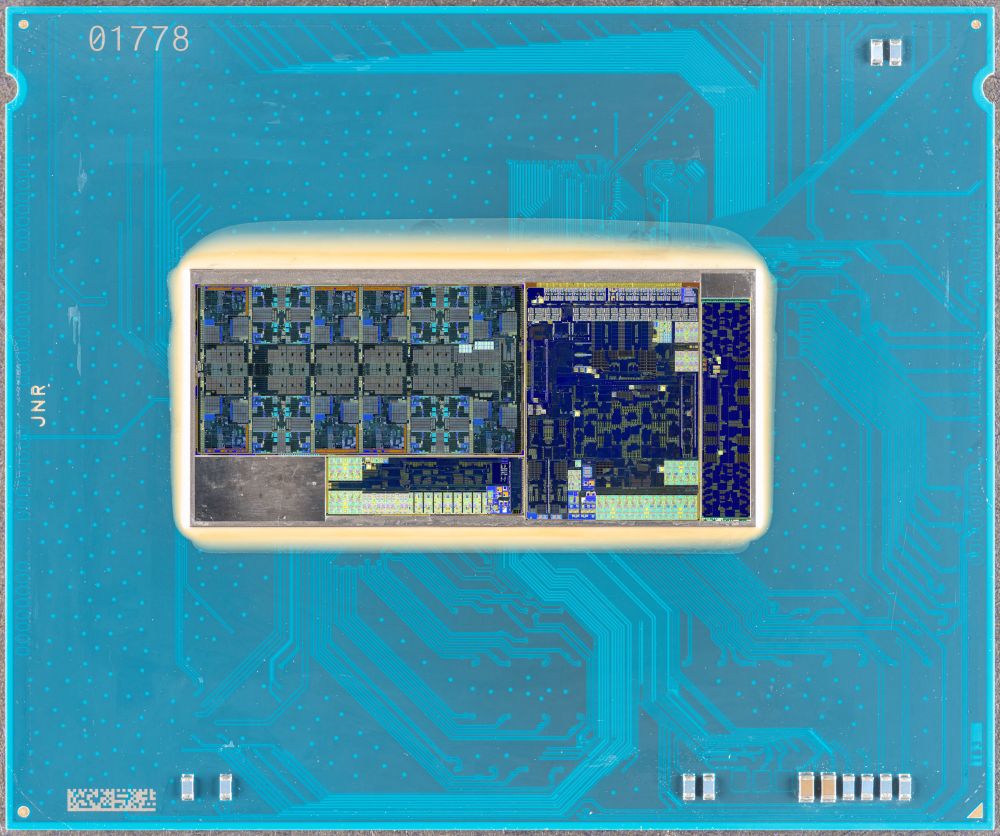

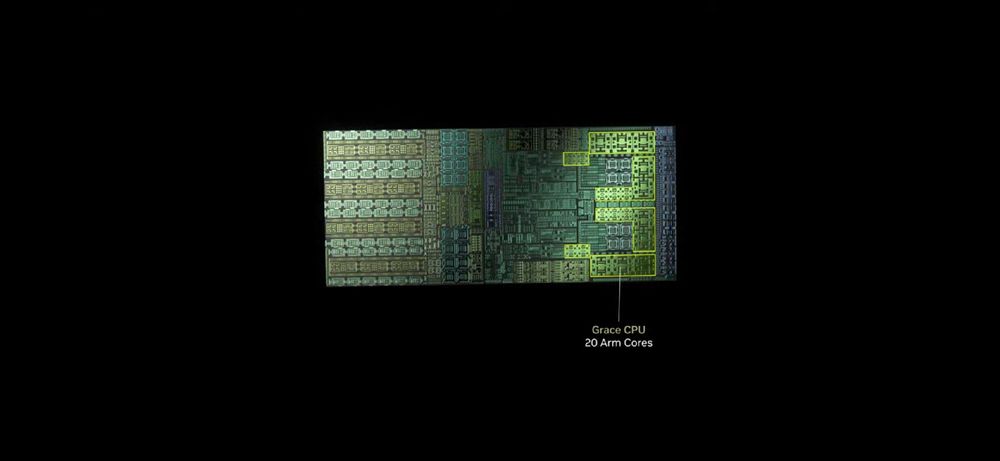

YouTube video by Geekerwan

This is Nintendo Switch 2's CPU!

this isn't clickbait, watch it before nintendo gets it taken down lol www.youtube.com/watch?v=3pr_...

07.05.2025 19:36 — 👍 184 🔁 33 💬 5 📌 1

Venice Classic SP8 → 8 CCD * 12 = 96 cores

Venice Dense SP7 → 8 CCD * 32 = 256 cores

?

🤔

Could more closely mirror Intel's 2 platform strategy, especially if SP8 supports 2P configurations

06.05.2025 22:47 — 👍 1 🔁 0 💬 0 📌 0

It seems there will be #AM5 #AMD #GorgonPoint as well

docs.amd.com/search/all?c...

29.04.2025 11:50 — 👍 6 🔁 3 💬 0 📌 1

Soon™ 🏹🌊👀

19.04.2025 22:25 — 👍 11 🔁 2 💬 1 📌 0

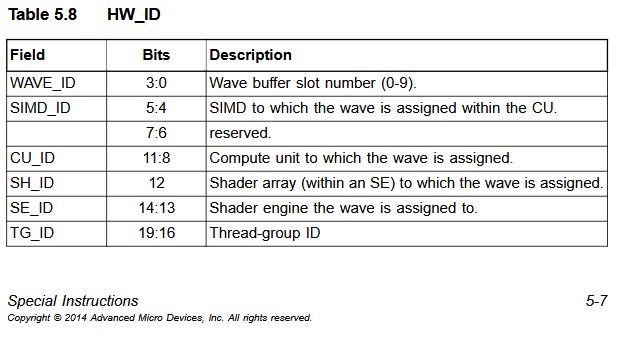

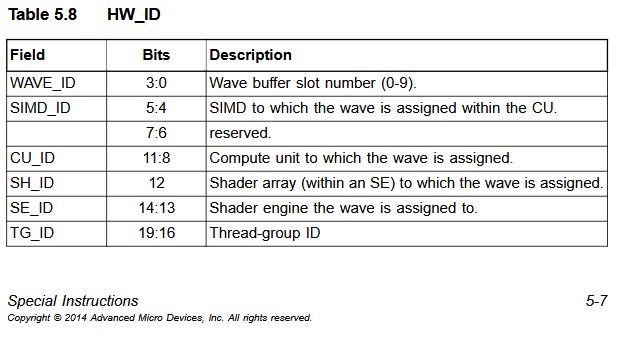

AMD had a separate Shader Array subdivision within Shader Engines even in the original GCN architecture. Interesting that it never mattered until RDNA added a L1 cache to the Shader Arrays and had multiple SAs per SE

13.04.2025 01:33 — 👍 2 🔁 1 💬 0 📌 0

An Interview with Zen Chief Architect Mike Clark

Zen is one of the most important microarchitectures in the history of the x86 ecosystem.

I recently had the honor of interviewing Zen’s chief architect Mike Clark! I tried to fit in as many microarchitecture questions as I could, including x64 vs ARM ISA power efficiency, 4k vs larger page sizes, 64-byte cache lines, scatter/gather and more:

www.computerenhance.com/p/an-intervi...

24.03.2025 18:51 — 👍 55 🔁 8 💬 5 📌 1

Good news: according to ark.intel.com, every #Intel #GraniteRapids-based #Xeon6 6900P, 6700P, 6500P SKU supports #AVX512 with dual 512bFMA, even the #GraniteRidgeD ones too

www.intel.com/content/www/...

25.02.2025 10:50 — 👍 4 🔁 1 💬 1 📌 1

Re: Nova Lake rumors

In before 8P16E dies get canned in favour of double 4P8E or 6P8E compute tiles for Nova Lake-S

I just can't take 2x8P16E at face value after the cancellation of 8P32E Arrow Lake

It's not like a 12P16E4e flagship with Big LLC would be *that* uncompetitive with Medusa, right?

08.02.2025 12:19 — 👍 0 🔁 0 💬 0 📌 0

Does anyone know why Apple did not release any chip pictures / die shots for the M4 series, like they usually do? I know there's a @techinsightsinc.bsky.social M4 die shot floating around, but I always enjoyed the images Apple released directly. Maybe someone has contacts at Apple?

03.02.2025 12:43 — 👍 4 🔁 1 💬 0 📌 0

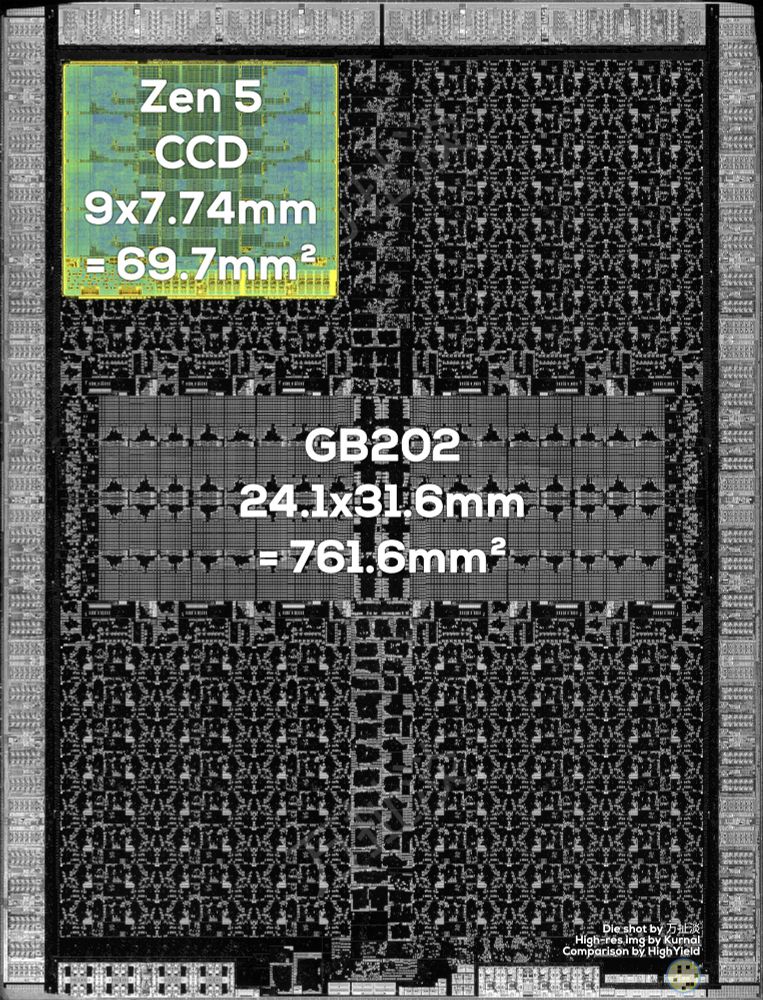

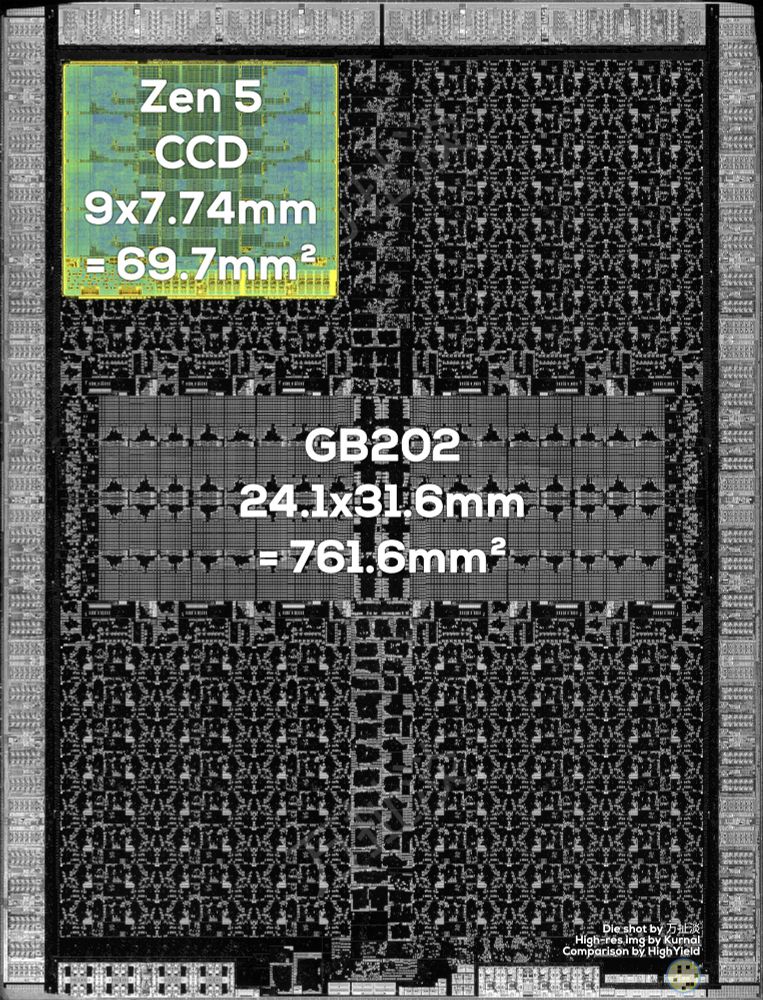

Visualizing the massive size difference between AMD's Zen 5 CCD & Nvidia's GB202.

29.01.2025 12:20 — 👍 11 🔁 4 💬 2 📌 0

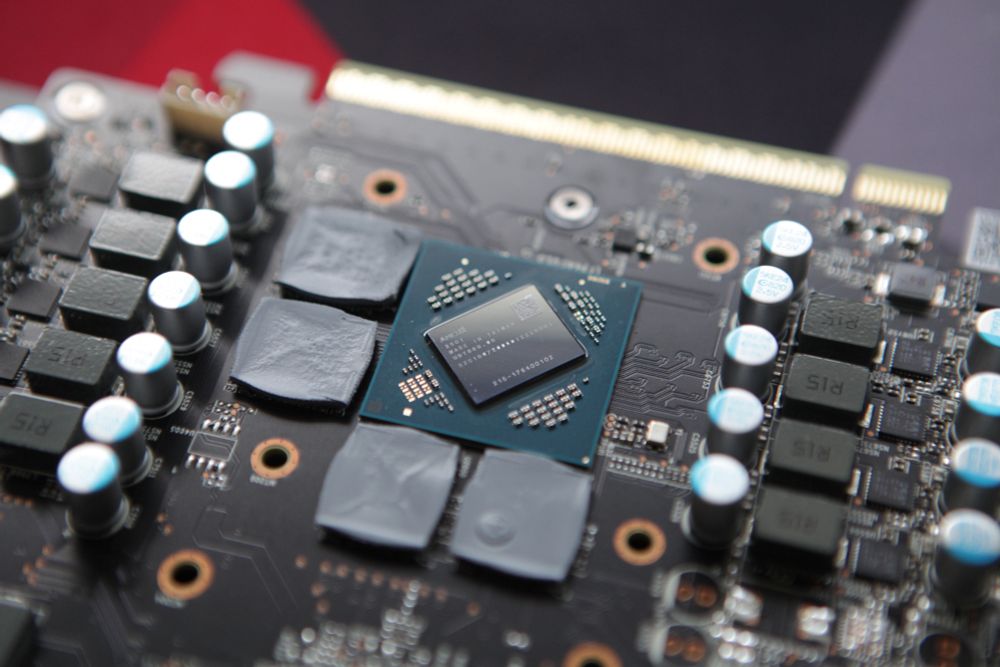

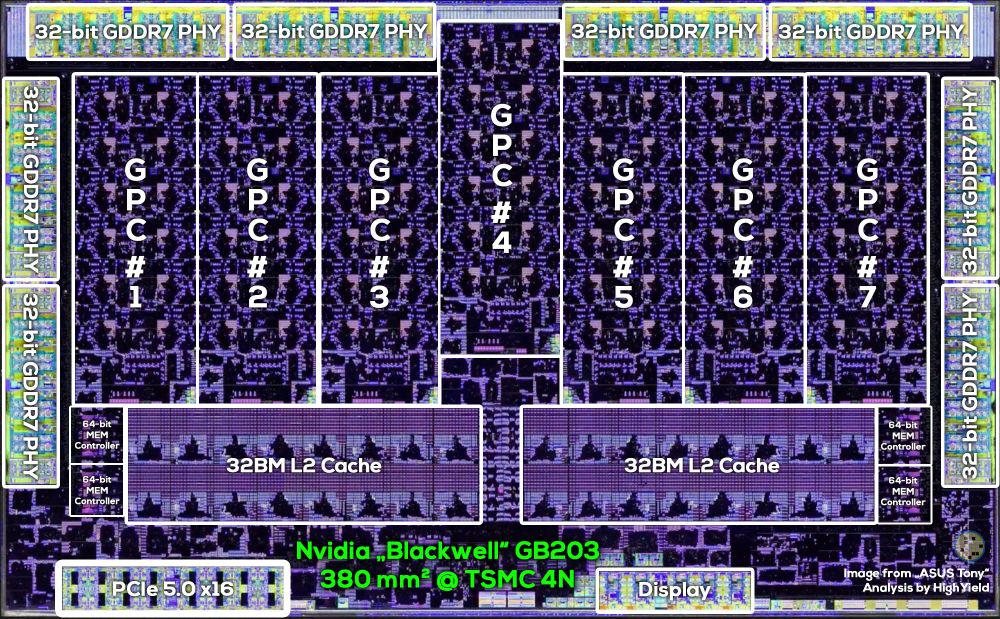

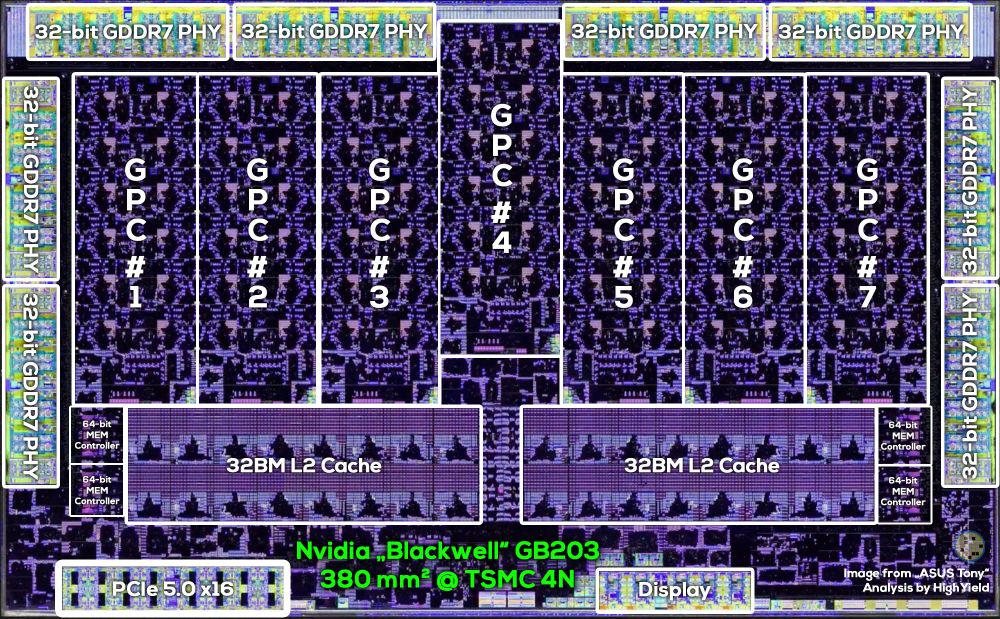

Here's a quick look at Nvidia's GB203, image from "ASUS Tony". Spec wise basically 1/2 GB202, but physically a different design and not just half of a GB202.

29.01.2025 17:33 — 👍 9 🔁 2 💬 2 📌 0

Is the fact that Samsung is only using the Snapdragon 8 Elite for the Galaxy S25 series a sign of strength for Qualcomm or a sign of weakness for Samsung's SoC team and Foundry? Or does it just not matter?

22.01.2025 19:12 — 👍 8 🔁 1 💬 0 📌 0

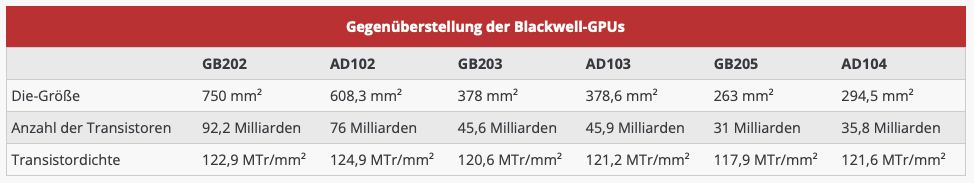

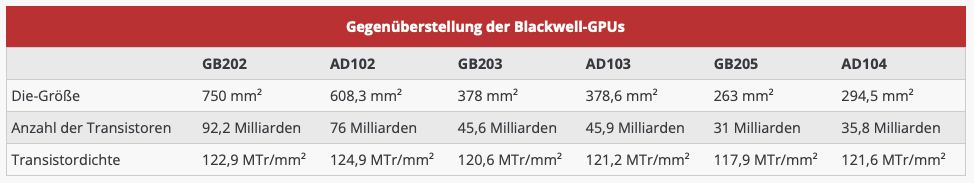

Transistor count and die size for GB202, GB203 and GB205 aka Blackwell. Those and the predecessors are all manufactured in TSMC 4N.

Source: www.hardwareluxx.de/index.php/ar...

15.01.2025 16:02 — 👍 3 🔁 1 💬 1 📌 2

"380 Ray tracing TFLOPS" will be on the list of things that drive me to be committed

07.01.2025 15:45 — 👍 9 🔁 2 💬 1 📌 1

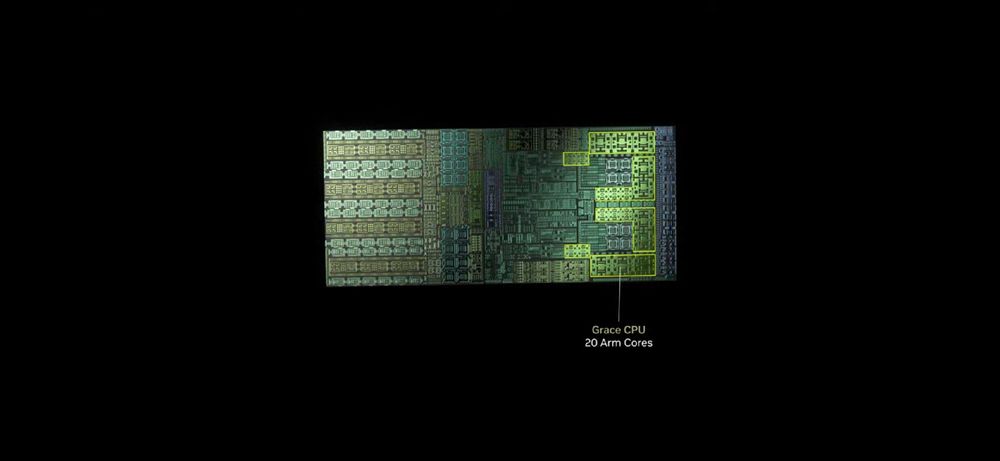

Is GB10 the high-end NVIDIA Laptop SoC?

Because otherwise why would it have an asymmetric CPU layout?

Looks like 2 clusters with 5x Cortex-X + 5x Cortex-A each

It also seems to have all the I/O you'd want for a Laptop

"1000 FP4 TOPS" (24TPCs?) would correspond GB205 (5070Ti Laptop) performance

07.01.2025 04:33 — 👍 0 🔁 0 💬 0 📌 0

Has anyone been able to find the actual document? There’s no link in the article, no link in the press release, no document in their white paper or documentation section on their site…

Even the performance optimization manual is vaporware??

19.12.2024 17:21 — 👍 9 🔁 3 💬 1 📌 1

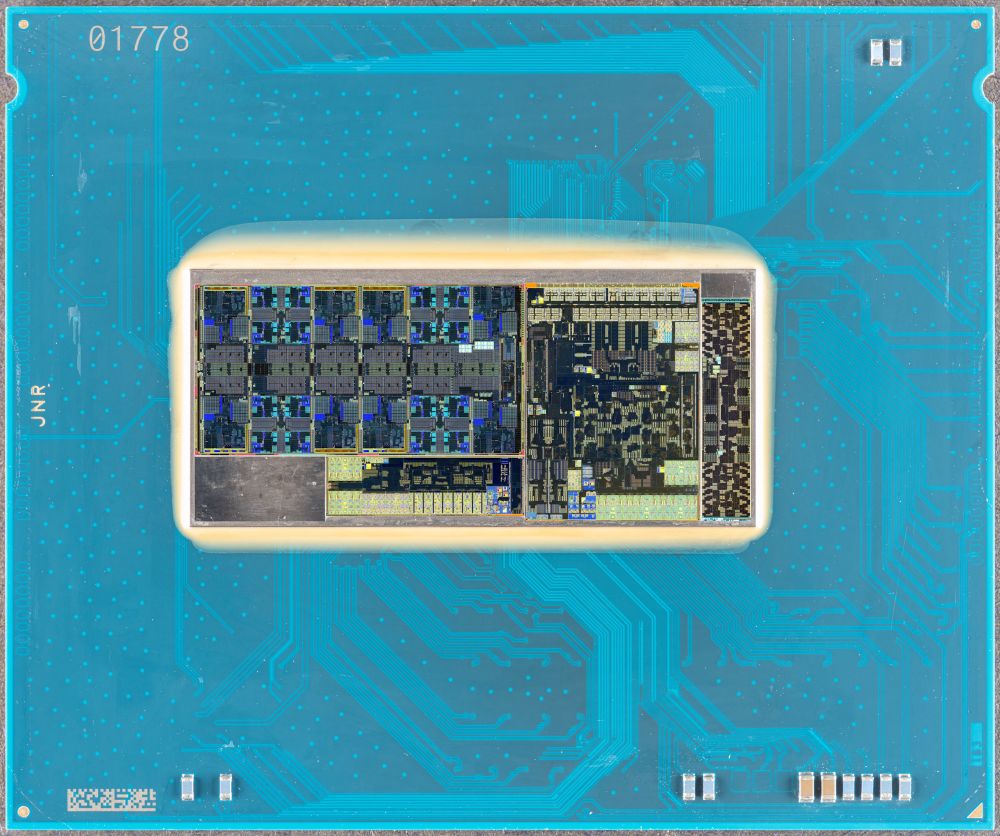

I wonder if the bigger Battlemage die (BMG-G31) could use this same package. There seems to be a lot of leftover space at the top-right, and package reuse would also mirror NVIDIA's strategy of having AD104 and AD103 share packages

03.12.2024 22:49 — 👍 1 🔁 0 💬 0 📌 0

YouTube video by High Yield

Why Hybrid Bonding is the Future of Packaging

Why Hybrid Bonding is the Future of Packaging

youtu.be/OlRLuajAgIc

01.12.2024 14:31 — 👍 13 🔁 3 💬 0 📌 1

I expect the Arc B580 to be around the A770 in performance, but have lower power consumption (somewhat closer to eg. 7600), as that would match the improvements we've seen with AMD going from N7- to N5-class nodes

That would still be terrible PPAC vs the competition though, so I'd hope for more

01.12.2024 13:36 — 👍 1 🔁 0 💬 0 📌 0

This account is run by Richard Stallman of GNU

Official account of the C Programming Language, invented by Immanuel Kant in 1799 at Bell Labs Königsberg

💀 The C Standard Cannot Be Replaced And Will Never Be Destroyed. 💀

✍ Writing: http://thephd.dev

📷 Avatar KIINGKISMET (https://kiingkiismet.com/)

🖼 Banner WusdisWusdat (https://wusdiswusdat.crd.co/)

Gamer who analyzes tech too much

Working on the next generation Z-series chip at IBM, opinions here are my own

Troublemaker | Computer Architect | @Arm Servers Architect @Google | Former DE @RedHat | Former VP @Nuvia_Inc | Runner | Author | All views my own | #ArmServers

HPC Architecture Ronin, currently at Nvidia. ex-MSFT, but forever a Crayon.

I am proud of my home state (MN) and you will hear about it.

All posts (especially the dumb ones) reflect my own positions and not that of my employer.

GPUs from fs to ms @ AMD / Interests: GFX, AI, RTL / Prev: AuthenTec (Digital HW), NASA, GaTech Grad, F1 fan. Views & statements are 100% mine.

Burrito scientist, AMD Infinity Fabric performance/architecture. An Olympic medalist once liked a picture of my dog pooping.

📍British Columbia

https://linktr.ee/philpark

Building computers for AI.

Formed in the summer of 2023, the UEC aims to develop a new standard for interconnection for AI and HPC datacenter needs, serving as a de-facto (if not de-jure) alternative to InfiniBand, which is largely under the control of NVIDIA these days.

I work on a YouTube channel.

Tech YouTuber. Everything silicon.

youtube.com/HighYield

Simple overclocking guides https://skatterbencher.com & https://youtube.com/skatterbencher

Official account.

Not all frames are created equal.

PC hardware rumors, leaks, and the latest news!

I create videos at Hardware Unboxed